超导量子芯片集成技术概述

时间:2023-06-09 10:15:29 来源:雅意学习网 本文已影响 人

郑伟文,李晓伟,熊康林,3,冯加贵,3

(1.量子科技长三角产业创新中心,江苏 苏州 215123;2.材料科学姑苏实验室,江苏 苏州 215123;3.中国科学院苏州纳米技术与纳米仿生研究所 纳米真空互联实验站,江苏 苏州 215123)

随着社会的发展,人类对于计算机计算速度和性能的要求不断在提升,未来数十年内,现有的电子计算机将无法满足人们在科研、商业等领域的需求。现阶段主要通过提高晶体管密度和缩小单个晶体管尺寸以提升芯片计算性能。而随着半导体技术的快速发展,硅基芯片已经到了3 nm 的技术节点,晶体管的沟道尺寸趋近于物理极限,基于经典物理的器件模型逐渐失效,量子隧穿现象将导致晶体管无法工作[1-5]。因此,利用先进封装[6]提升晶体管密度成为提高芯片性能最为可行的技术方案之一。

当前先进封装以Wire-Bonding、Flip-Chip 和TSV(Through Silicon Via)工艺为主要手段,极大提升芯片单位体积内晶体管数量,同时缩短不同芯片间的电学联通路径,以降低功耗并获得更大的带宽。然而,受到热量耗散问题的制约,封装并不能无限制地增加芯片中晶体管的数量和密度。芯片在工作状态下,除了材料本身的发热耗散外,根据Landauer 原理(每删除一比特的信息,需要消耗一定的能量),消耗的能量也都将转变为热量。如果芯片内积聚的热量无法快速向外耗散,将导致芯片温度快速升高而无法工作,因此传统芯片的集成度终将受到散热问题的限制。

与经典电子计算所不同,量子计算过程是可逆的,理论上热耗散极小;同时量子比特所独有的叠加态和纠缠态,使其计算能力随着比特数量的增加呈现指数增长。量子计算的概念,从20 世纪80 年代提出后,已经成为国际热点研究方向,目前已发展出了包括超导量子、光子、离子阱、量子点等众多的量子技术路线。而在这众多的技术路线中,由于超导量子方向与传统半导体技术的兼容性强(包括设备、工艺、材料等与目前的半导体通用),因此相较于其他技术路线,超导量子比特的制备和可扩展性都具有较大优势,成为世界各大科技公司和科研单位的主要研究方向。例如IBM 公司推出的目前最先进的127 量子比特芯片、D Wave 公司推出的5000 比特的量子退火机都采用了超导量子方案。

本文将着重介绍超导量子在可扩展技术上的发展方向和技术路线,利用先进封装技术实现超导量子芯片比特数量从10 量级到1000 量级的突破,甚至于通过一种可扩展模块化集成方式实现最终的通用量子计算。同时分析了各种先进集成技术在超导量子芯片扩展中的作用以及所面临的挑战。

超导量子芯片需要在极低温(约10 mK)环境下工作,以降低环境噪声对比特的影响。超导量子比特工作原理是利用约瑟夫森结在极低温环境下的非线性电路特性,构建不同能级间距的能级态,并选择其基态和第一激发态构成二能级系统。

在传统半导体芯片中,通过外端输入的电压信号对晶体管进行开关控制从而实现0 和1 的转变。在超导量子芯片中,量子比特需要通过微波信号进行调控其基态和激发态。而多个量子比特要实现协同工作,需要通过电容、电感或谐振器进行相互耦合。由于量子比特信息具备不可复制性,单个量子比特需要足够的时间进行独立操作计算,所以量子比特的相干时间是其核心指标之一。目前超导量子最长的相干时间在1 ms 左右,而单次的比特操作时间最短在10 ns 级,理论上可以实现103~104次的操作。

除了比特的质量,比特的数量同样重要,否则在比特相干时间内无法完成大量的计算。相较于成熟的传统半导体芯片,超导量子芯片目前还处于初始阶段,比特数量主要集中在10~100。同时,在超导量子芯片中,除了约瑟夫森结(尺寸在100~1000 nm),还需要控制线、谐振器、电容电感、读出线等结构(单个结构的尺寸在100~1000 μm 量级),考虑到电磁场的串扰影响,各结构间都要保留足够的间隔。想要制备100 数量级的量子比特,在单个100 mm2量级尺寸的芯片平面上已经无法实现。因此,借鉴传统半导体的发展路线,量子比特的先进封装集成是最为有效的方案之一。

传统半导体封装,侧重于不同功能器件的模组化,从而实现芯片功能化的集成以及物理保护。而超导量子比特中的封装集成,主要解决芯片平面布线空间不足问题。由于量子比特本身比较脆弱,对环境噪声十分敏感,同时又采用微波信号进行操控读取,因此在考虑量子比特的集成时,对材料、线路结构设计以及工艺有更高的要求,同时还需要考虑电磁干扰以及信号衰减。下面将按照量子比特数量从10 量级到1000量级,再到通用量子计算机的路线,分别介绍平面工艺、倒装焊工艺、TSV 以及模块化在各阶段的作用以及所面临的挑战。

2.1 平面工艺

稀释制冷机是目前唯一能满足超导量子芯片工作温度需求的设备,但其内部空间极为有限。超导量子芯片需要排布大量的测控线,芯片的尺寸一般为100 mm2量级。当量子比特数量较少时(小于20),一般采用单平面排布设计。但此时需要对线路的排布进行优化,以降低各线路之间的影响。目前最常用的方式就是采用空桥方案,利用架空的超导传输线相互接地,以实现降低线路间的干扰以及节省线路排布空间的目的,如图1 所示[7]。

图1 空桥结构示意图。(a)谐振腔和空桥结构;(b)SiO2做牺牲层的空桥结构;(c)HF 气相释放去除SiO2层后空桥结构[7]Fig.1 Schematic of air-bridge structure.(a) Resonator and air-bridge;(b) Air-bridge structure with SiO2 sacrificial layer;(c) Air-bridge after SiO2 layer is removed by VHF release[7]

2.2 倒装焊

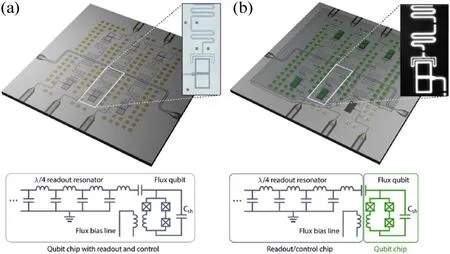

随着量子比特数量增加(20~50 比特),单平面已无法满足排线空间需求。参考目前传统半导体的做法,可以向第3 个维度发展,即3D 集成。由于超导量子线路结构大多通过电容电感耦合的方式进行连接,因此可以将线路拆成2 个平面,利用Flip-Chip 模式进行连接。目前常见的是将量子比特和读出控制分成2 个单独的平面,再利用电容电感进行耦合连接,同时利用超导金属作为机械支撑和信号连通,如图2 所示[8]。为了实现芯片低温超导,芯片线路材料必须都为超导体,因此需要选择合适的超导金属作为上下芯片连接层。而超导线路中Al/Al2O3/Al 结构的约瑟夫森结,膜厚在100 nm 级别,结构十分脆弱,高温及腐蚀性环境都对其具有很强的破坏性。因此作为连接层的金属必须可以在较低的温度下进行压焊连接,同时在超低温下能有较好的机械性能。参考目前半导体中的应用,In 是较为合适的选择。由于整个线路必须满足超导性,因此不同材料之间的界面问题是该封装技术的难点之一。一般通过对基体表面进行Ion Milling 处理,以达到去除氧化层的目的;同时也会在In 和基体材料(如Al、Ta、Nb 等超导金属薄膜)之间做一层超导的UBM(Under Bump Metal)作为粘附层和阻挡层,用以增加In和基体材料之间的结合力,并防止形成金属间化合物。

图2 常规及倒装焊比特芯片及电路示意图。(a)常规6 比特芯片示意图;(b)比特芯片倒装焊结构电路示意图[8]Fig.2 Standard and flipped qubit chip configurations.(a) Schematic of standard qubit chip with six capacitively shunted flux qubits;(b) Schematic of a flip-chip qubit chip[8]

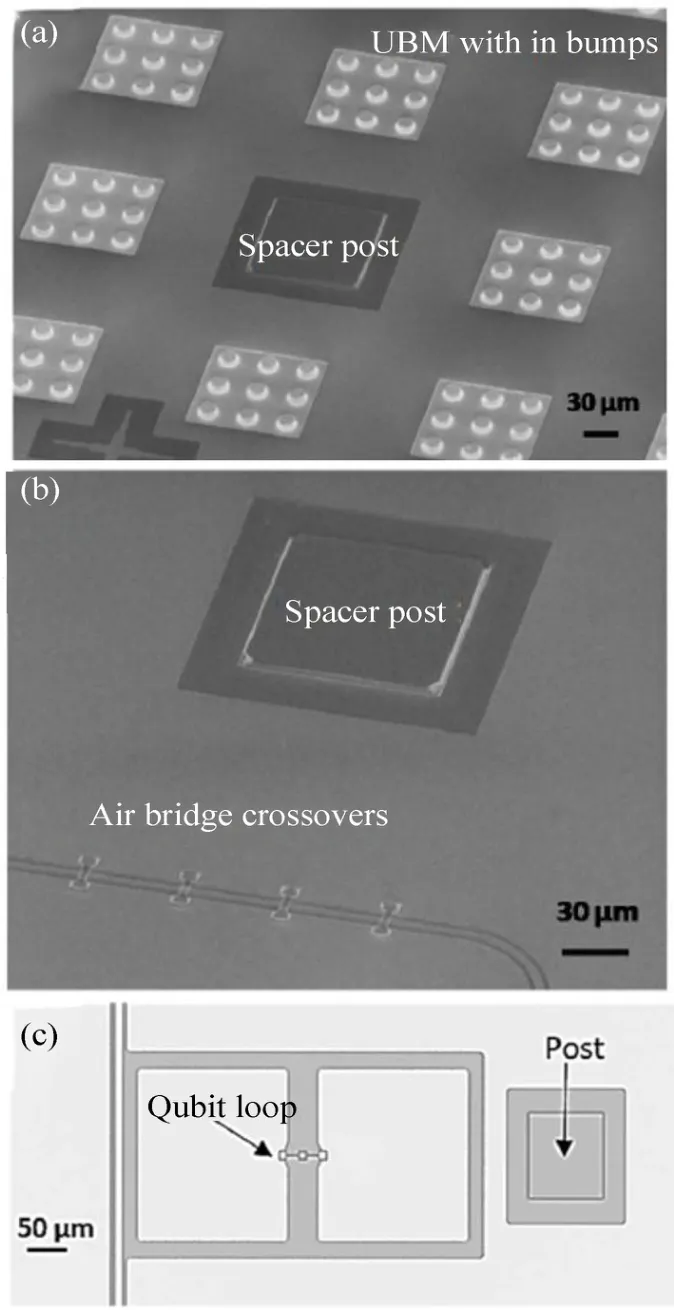

除了要处理不同材料间的界面问题,上下层芯片的间距需要严格按照设计要求进行控制,以满足电性设计标准。有人提出通过在硅片上刻蚀出2~4 μm 高的硅柱,用以限制压焊过程铟柱的压缩量,如图3 所示[9]。由于硅柱的存在,上下芯片的间距得到了有效控制,同时芯片不同位置的翘曲也得到有效改善,可以做到平均值11 μrad 的水准[9]。在不引入对电磁场过多干扰的前提下,通过其他手段进行间距的控制,理论上同样可行。

图3 在倒装焊工艺中控制芯片间距的硅柱。(a)硅柱分布在焊点附近;(b)硅柱分布在空桥附近;(c)硅柱分布在约瑟夫森结附近[9]Fig.3 Images of flip-chip process integration with Si spacer posts.(a)Si spacer posts near bumps;(b) Si spacer posts near empty air-bridge;(c) Si spacer posts near Josephson junction[9]

2.3 TSV 多层堆叠

当比特数量继续增加(100 数量级),上下2 层结构也无法满足排线的空间需求,此时需要更多的平面进行比特的扩展,TSV 工艺将发挥其巨大的优势。利用TSV 贯穿Wafer 正反面,将两面的图形结构线路通过TSV 内的导线进行连通,再利用Flip-Chip 与第2个芯片进行连接[10-14]。TSV 工艺的优点十分明显,通过Wafer 内部穿孔进行正反面的连接,不仅充分利用了Wafer 的正反面空间,同时解决了排线密集占空间的问题。然而,相较于传统半导体封装技术中的TSV工艺,超导量子中的TSV 工艺有更多的难点需要克服:

(1)TSV AR(深度尺寸∶开口尺寸)高: 目前传统半导体封装技术中,TSV 的开口尺寸在几微米到几百微米不等,同时Wafer 减薄厚度在几十微米,一般AR<10,主要目的是为了缩短不同芯片垂直方向电学信号传输路径,降低信号损失和功耗。然而,在超导量子芯片中,为了减少比特和其他结构的相互影响,彼此距离需要尽可能大。同时为了减少TSV 的占地面积及对结构的影响,需要其开口尺寸尽可能小。为此,在超导量子芯片中TSV 的AR 普遍在10~20,甚至更高。此外,为了有利于后续孔内超导材料的生长覆盖,要求孔内侧壁尽可能光滑,这对工艺提出了苛刻的要求。

(2)TSV 超导金属生长: 传统半导体TSV 工艺中主要以铜作为连通导电材料,采用电镀工艺进行从底到顶的完全填充。一般工艺顺序是先生长一层SiO2作为绝缘层,然后生长一层TiN 作为粘附层和阻挡层,再生长一层Cu 作为种子层,最后进行电镀。由于半导体产业发展迅猛,相应的技术都得到了很好的发展和优化,即使对于AR 超过10~20 的TSV 电镀铜工艺,通过优化也能满足要求。但在超导量子领域,相应的技术十分有限,尤其是针对超导金属的电镀工艺更是缺乏研究。而类似PVD、CVD 等薄膜生长工艺也很难做到高AR 的TSV 填充。目前最有效的薄膜生长手段是ALD 工艺,理论上可以达到100%的覆盖均匀性。但ALD 最大的缺点是生长速率慢,以生长TiN[15-19]为例,一般在0.3~1 A/cycle,平均生长速率在10~15 nm/H。而为了保证信号传输,TSV 孔内金属最薄厚度要求大于50~100 nm。

MIT 对超导量子TSV 相关工艺进行过研究分析,利用Interposer 进行正反面图形结构化,再插入到Qubit-Chip 和SMCM (Superconductor Multilayer Chip Module)之间进行焊接连通[20-23],如图4 所示[23]。在该方案中,比特主要集中在上面的Qubit Chip 上,通过Interposer 上的Coupler 或者Qubit 进行耦合,再利用TSV 内的导线连通到背面,最后通过铟柱连接下面的SMCM。

图4 TSV 工艺三层堆叠封装示意图。(a)超导量子芯片三层封装示意图;(b)Interposer层上各功能结构区示意图[23]Fig.4 Schematic of TSV process in three-layer stack integration.(a) Schematic of superconducting quantum chip three-layer stack integration;(b) Schematic of each functional structure area on interposer layer[23]

IBM 近期公布了其最先进的超导量子计算机127比特的Eagle 模型、相关性能参数及技术迭代图,如图5 和6 所示[24]。与预期结果一致,其采用了TSV 和多层布线技术(MLW),将量子比特、读出谐振器以及测控机构分成3 部分,再利用Flip-Chip 技术进行多层互联。在IBM 公布的性能参数分析中也指出,串扰是多比特计算机面临的一大挑战,而TSV 和MLW 能提供天然的串扰屏蔽,有效改善串扰问题。

图5 Eagle 模型图[24]Fig.5 Eagle modle[24]

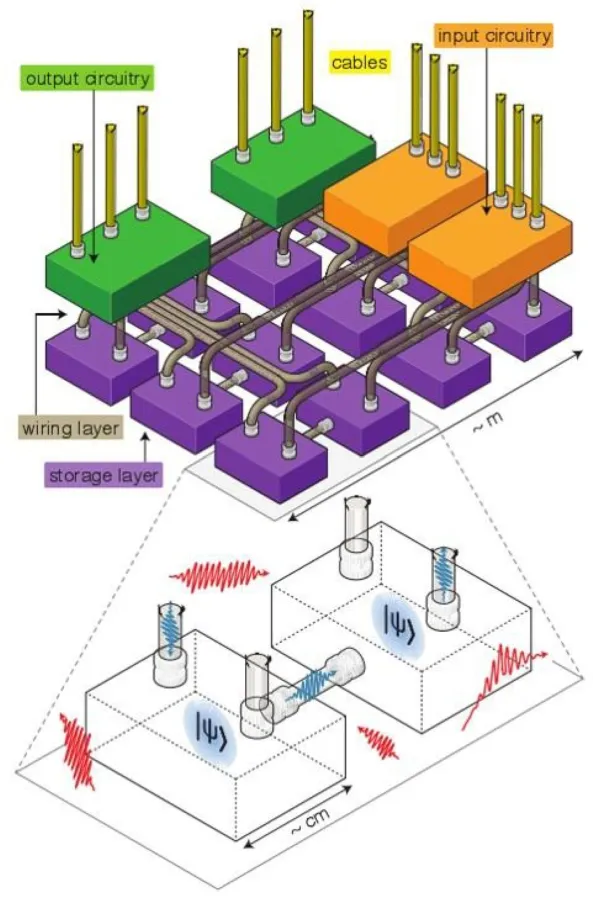

2.4 模块化集成

如果量子比特数量继续增加到1000 数量级,或许可以通过增加Interposer 的层数进行缓解[25-27]。此时,Interposer 的正反面都需要做上结构以充分利用空间。当量子计算机比特数量发展到了1000 量级,已经可以实现初步的商业应用,而要实现通用的量子计算,则需要百万数量的量子比特。鉴于目前超导量子比特还处于100 量级阶段,除非有了突破性的发展,或许还需要数十年时间才能达到通用计算的应用。耶鲁大学曾提出一种可扩展量子计算的多层微波集成量子电路,以实现可能的通用量子计算,如图7 和8 所示[28]。这种设计与目前的传统计算机模块类似,各个功能模块实现自身屏蔽并相互独立,利用单独的通道进行连接。然而目前这种设计还处于概念阶段,相关材料及设计优化是最大的瓶颈。

图6 IBM 超导量子计算机技术迭代图[24]Fig.6 Technology iteration diagram of IBM superconducting quantum computer[24]

图7 一种可扩展的量子信息处理器草图[28]Fig.7 Conceptual sketch of a quantum information processing device suitable for scaling[28]

从量子计算概念的提出到现在经历了近40 年,算法和硬件方面都得到了极大的发展。尤其是在近20 年,超导量子进入了快速发展通道,俨然成为最有希望实现通用量子计算的技术方案。超导量子比特的相干时间由最初的ns 级别发展到现今的100 μs 级别,单/双比特门的保真度达到了最低阈值,比特数量也达到了100 量级。根据IBM 的技术路线,将于近2 年内实现1000 比特,10 年内实现百万比特的通用量子计算机。

图8 一种可扩展量子计算的多层微波集成量子电路示意图。(a)集成电路各功能区示意图;(b)矩形腔体式谐振腔的截面结构示意图;(c)超导传输线及比特在屏蔽腔体内的结构分布示意图[28]Fig.8 Schematic of a multilayer microwave integrated quantum circuit.(a) Schematic of the functional regions of the integrated circuit;(b) Schematic of the cross-section structure of the rectangular cavity;(c) Schematic of the structure distribution of superconducting transmission lines and bits in the shielded cavity[28]

鉴于传统半导体的发展路线和超导量子的发展趋势,在未来10 年内先进的封装集成技术将是超导量子计算机的主要技术发展方向之一。Flip-Chip 和TSV技术有望将比特规模提升至1000 量级,可实现超导量子计算机的初步商业化应用。而要实现百万比特的通用量子计算机,除了新一代的理论发展或者封装集成技术外,还需要极力发展低温制冷设备以满足芯片体积和大量的测控线的空间需求。

随着Google 和IBM 等科技公司纷纷公布在超导量子计算机领域取得的优异成果,让人们看到了超导量子计算机的优越性及商用化的可能性,促使更多的科技公司和科研院所参与研究,促进了行业的蓬勃发展。相信可商用化的超导量子计算机在不久的将来将成为现实。

猜你喜欢 量级示意图比特 先画示意图再解答问题数学小灵通(1-2年级)(2020年9期)2020-10-27黔西南州旅游示意图当代贵州(2019年41期)2019-12-13比特币还能投资吗海峡姐妹(2017年10期)2017-12-19比特币分裂三联生活周刊(2017年33期)2017-08-1121连胜环球时报(2017-03-13)2017-03-13比特币一年涨135%重回5530元银行家(2017年1期)2017-02-15神秘的比特币CHIP新电脑(2014年8期)2014-08-13“三定两标”作好图中学生数理化·八年级物理人教版(2014年2期)2014-04-02中缅油气管道示意图环球时报(2009-09-09)2009-09-09