一种用于PCIe,多通道的De-skew,电路设计

时间:2023-06-20 11:45:03 来源:雅意学习网 本文已影响 人

王可扬,吉兵,屈凌翔

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

PCI-Express(Peripheral Component Interconnect Express,PCIe)作为第三代高性能通用I/O 总线技术,可以视作是PCI 总线的改进版本。它不单继承了PCI 的一些良好特性,实现了PCI 总线协议全部软件的向下兼容[1-2],同时,在总线结构上进行了革命性的改变:一是从并行式变为了串行式,二是采用了点对点的互连技术[3]。此外,PCIe也支持如热插拔、功耗管理、质量服务等高级特性[4]。

目前PCIe5.0 可支持最快32 GT/s 的传输速率,同时,不仅支持单通道数据传输,也可以支持2 路、4 路、甚至32 路的多通道数据传输。然而,在PCIe 进行多通道数据传输时,即使使用同样的时钟源从发送端进行数据发送,如果不在接收端进行处理,仍然无法保证所有通道的数据能够同时抵达接收端[5]。因此各个通道间就会存在时差,这是因为实际电路中存在数据的传输延时。导致延时的因素有:(1)各通道信号线的长度不同;

(2)线路板在印刷时的阻抗存在差别;

(3)由于数据的串化和解串引入延迟;

(4)外部因素例如温度的影响等[6-7]。

因为各通道的延时来源不尽相同,必然会使得各通道上的延时也有所区别。这也给消除多通道数据传输的延时误差带来了更大的设计压力。图1 所示为以四通道为例的情况。

如图1 所示,接收端在接收到各通道传送来的数据后需要经过反数据剥解逻辑,即由数据发送时的剥解顺序来进行数据合并。如果各通道上的数据在同一时间点并未对齐,那么接收端就无法正确地进行数据合并,从而产生顺序混乱的数据包并发送到数据链路层。这是不被允许的,所以接收端必须对各通道间的相位偏移进行消除,以保证多通道数据能够在同一时间点到达接收端进行后续处理。该过程被称为链路的多通道纠偏(Laneto-Lane De-skew),图2 所示为四通道的De-skew 过程。

图1 数据传输中产生的skew 现象

图2 接收端的De-skew 处理

本文提出了一种De-skew 逻辑电路设计,能够在不预先知晓哪路数据先到达的情况下消除各通道间的偏移现象,同时满足通道间skew 最大值的约束要求。该逻辑方案也可以应用于PCIe 以外的其他任何电路中多通道间相位偏移的处理。

1.1 常见De-skew 实现方法

PCIe 协议规范中对多通道De-skew 做了一些规则要求,但并未规定实现De-skew 的具体方法。目前主要的实现方法是借助TS1/TS2 以及FTS 等有序集。因为这些有序集具有特定的结构和长度,且在所有通道上遵循同时发送的规则,因此可以用来作为衡量各通道间偏移量的标志。在PCIe 协议规范中,针对第一代/第二代(Generation one/Generation two,Gen1/Gen2)和第三代/第四代(Generation three/Generation four,Gen3/Gen4)所要实现的De-skew,建议利用不同的有序集,具体如下[8]:

(1)Gen1/Gen2 中建议使用以下一个或多个作为衡量标志:TS1/TS2 有序集的COM 字符(有序集的头字节)、EIEOS 有序集的COM 字符、在FTS 序列后紧接着的第一个SKP 有序集的COM 字符、不使用SRIS 时在训练序列中的SKP 有序集的COM 字符。

(2)Gen3/Gen4 中建议使用以下一个或多个作为衡量标志:SDS 有序集、退出L0s 状态时的EIEOS 有序集、Gen3 时的SKP 有序集、Gen4 时的FTS 序列后紧跟的第一个SKP 有序集。

目前,国内外常见的De-skew 电路设计思路多是利用计数器和多个寄存器进行设计实现。该方法使用多个寄存器进行数据的缓存移位,每两个寄存器间加一个选择器用来控制数据是否进入寄存器进行缓存。同时,在每条通道上添加一个计数器,当每一路的数据到达第一个寄存器时就开始计数[9]。计数器可以用来观察各条通道上的数据何时到达,也可以观察各通道数据分别经过了多少个寄存器。更重要的是,通过各通道计数器的数值做差可以算出各通道间的skew 大小并判断其是否超过所允许的最大值。但该方法实现需要的寄存器数量较多,尤其在Gen3/Gen4 速率下,由于每秒内传输数据量的加大,代码实现会更为冗长复杂。即使速率不变,随着设计频率以及数据位宽的改变,寄存器数量也会发生改变,因而整个De-skew 代码的实现需要进行大量变动。针对上述问题,本文提出了一种新颖的逻辑设计,可有效降低逻辑设计的复杂度,同时拥有很强的代码复用性。

1.2 利用FIFO 的De-skew 逻辑设计

针对如何消除多通道的skew 问题,本文提出了一种利用同步FIFO 实现De-skew 的逻辑电路。

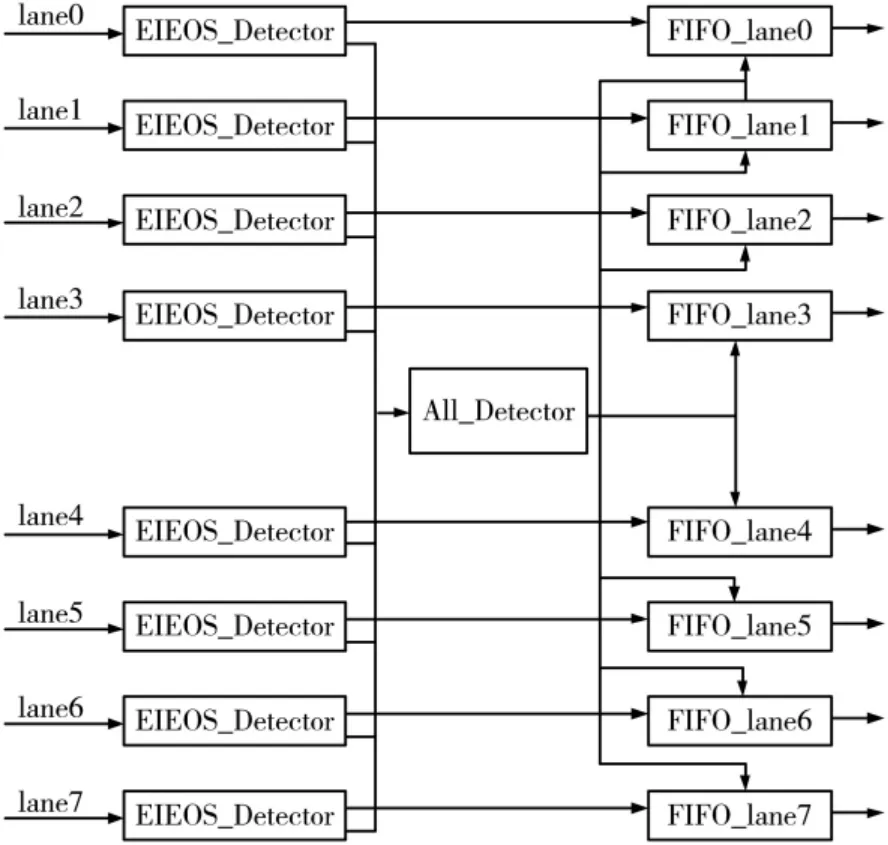

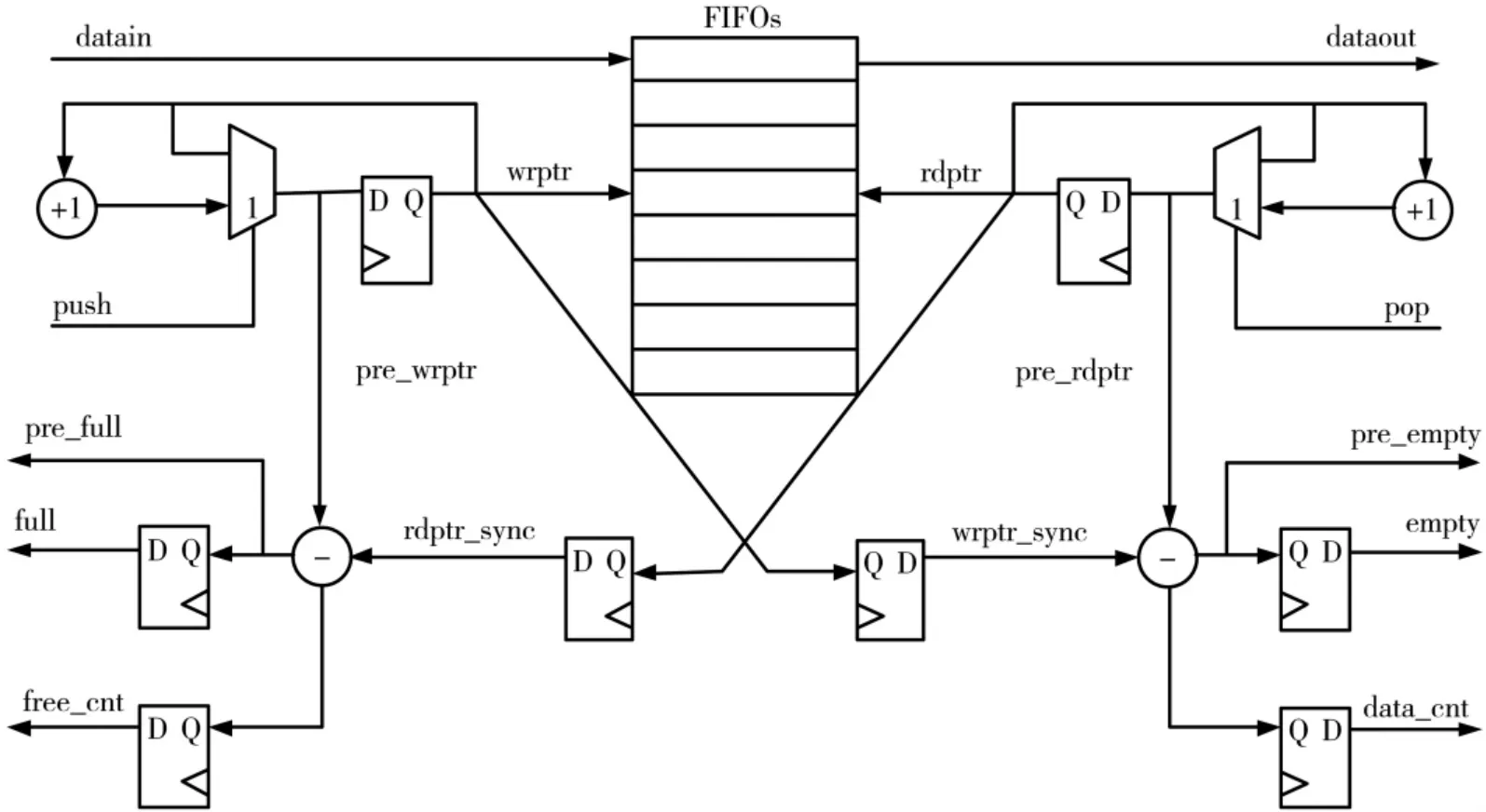

以Gen3 速率下的八通道传输情况为例,结构如图3所示。在每条通道后接入一个同步FIFO(FIFO 结构如图4所示),FIFO 作为一种先进先出的数据寄存器,保证了数据流按顺序写入且按顺序读出。在此基础上,本文所提出的FIFO 结构还能够准确地对FIFO 的空/满状态进行判断,以保证数据正确地写入或者读出。具体实现方式为:采用EIEOS 有序集作为Gen3 条件下的De-skew 衡量标志,当某条通道上检测到EIEOS 的有序集时,该通道的FIFO 便会将push 信号拉高,此时通道上的数据块将会被写入到FIFO 中进行暂时的缓存。当所有通道上FIFO 的push 信号均被拉高时,即所有通道均检测到EIEOS 有序集且每条通道上的数据块均已写入各个FIFO中后,将所有通道上FIFO 的pop 信号同时进行拉高。这样,所有通道将同时输出EIEOS 有序集以及之后的所有数据块,从而实现了各条通道数据的对齐校正功能,完成了通道的De-skew。

图3 利用FIFO 的De-skew 逻辑电路

图4 FIFO 结构图

值得注意的是,该逻辑电路所使用的FIFO 支持位宽和深度的自由配置。通过对这两个参数的配置,进而满足各种不同数据传输速率下的De-skew 需求。在本设计中,设备工作在Gen3 条件下,每条通道的数据位宽为32 bit,时钟频率为250 MHz,规定各条通道间的skew 最大值为32 ns。因此FIFO 的位宽设置为32 bit,并合理设置FIFO 的深度(Deepth)使之能够满足最大skew 值的要求。由于此时传输的数据流中每个symbol(字符,长度为8 bit)对应的传输时间为1 ns,则各条通道间的skew 最大为32 个symbol 的位置。此时FIFO 的位宽为32 bit,即4 个symbol 的大小。将FIFO 的深度设置为8,这样FIFO中能够缓存的数据最多为32 个symbol,从而确保了最大skew 值的要求。假设lane0 的数据流最先到达接收端并被push 进其对应的FIFO 中。而lane7 的数据流则比lane0 要晚到36 ns,即36 个symbol 的位置。这样当lane7的数据流到达接收端并被push 进其对应的FIFO时,lane0 上的FIFO 已经被填满。而此时因为8 条通道的push 并未全部完成,各FIFO 的pop 信号不会被拉高,lane0 会同lane7 一起往各自FIFO 中送入数据,这会造成lane0 的FIFO 的数据溢出,产生错误,进而产生De-skew错误信号。De-skew 错误信号会通知发送端重新进行数据发送,直到通道间skew 不超过最大规定值,或者超时传输终止。

针对前文所述的传输情况:时钟频率为500 MHz、数据位宽为8 bit、最大skew 值为20 ns 的Gen2 速率,只要将FIFO 配置为位宽为8 bit,深度为10,同时将EIEOS有序集的检测改为对COM 字符的检测,便能够轻松实现该情况下的De-skew 设计。因此,本文提出的逻辑电路结构不仅具有全面性和可实现性,还具有很好的代码复用性。

本文采用Synopsys 公司的PCIe VIP 以及AMBA AXI VIP 搭建了验证平台。VIP 作为验证知识产权模块,它是一种预先验证过的内建验证结构,能够提供完整且灵活的应用机制。通常,VIP 是基于标准协议的,可以很方便地将其插入到基于仿真的确认测试中,从而显著提高验证的可复用性及验证效率。PCIe 控制器可以作为RC(根联合体)或者EP(终点设备),将PCIe VIP 作为RC,而将待测设计作为EP 进行验证。

基于所搭建的验证平台,本文采用Synopsys 公司的仿真工具以及Novas 公司的Verdi 工具进行了仿真联调。图5 为对逻辑电路进行验证仿真的波形。此时的输入数据为连续4 个64′hffff_0000,即为Gen3 条件下的EIEOS 有序集。从图3 中可以看到,输入8 条通道的数据中,EIEOS 有序集并未对齐,而经过该De-skew 逻辑电路后最终的输出数据——8 条通道的EIEOS 有序集完成了对齐。仿真结果验证了该De-skew 逻辑电路功能的正确性和可行性。

图5 De-skew 功能仿真图

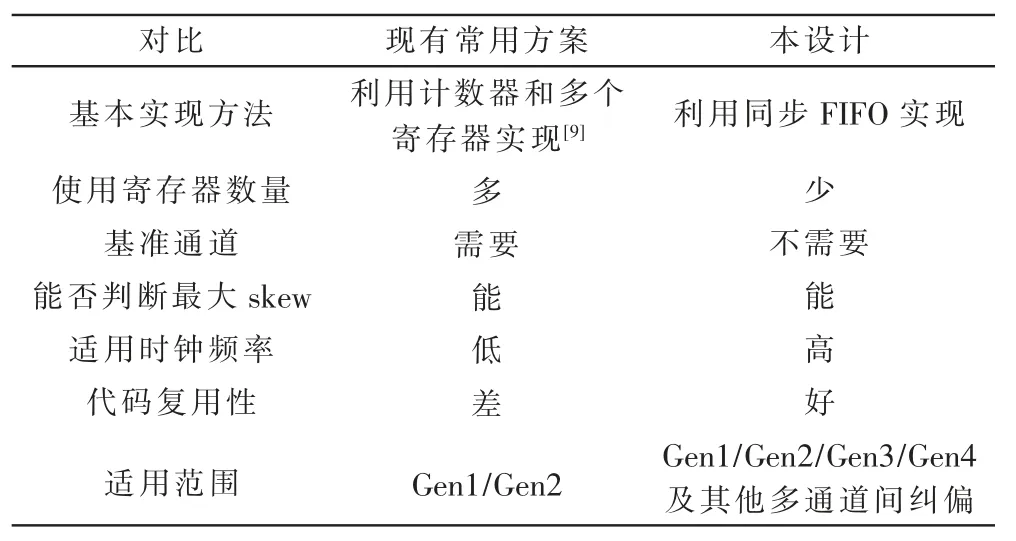

表1 所示为本文De-skew 逻辑设计方案同现有常用方案的对比,可以看到,虽然利用计数器和多个寄存器进行数据缓存的方案也能正确实现De-skew 功能,并对通道间skew 是否超过最大规定值进行判断,但本文提出的方案更为简便,代码量更少,通过配置FIFO 的位宽和深度也能适用于Gen3/Gen4 等更高的速率情况,具有全面性、优越性和可复用性。

表1 De-skew 逻辑电路方案对比

由于PCIe 多通道间的延迟差异,必然会导致数据传输中的skew 现象。本文提出了一种逻辑电路,在通道数据到达接收端的先后顺序未知的情况下,实现De-skew功能,同时满足PCIe 规定的最大skew 值需求。最后搭建测试平台并通过仿真验证了该逻辑设计方案。结果表明,本文所提出的逻辑设计有效实现了PCIe 多通道的De-skew 功能,同时,该逻辑电路具有普适性,能够适用于PCIe 的各种速率、位宽、时钟频率等搭配情况,可应用于其他高速电路的多通道传输。本设计为消除通道间的skew 问题提供了良好的借鉴意义。

猜你喜欢 逻辑电路接收端寄存器 基于扰动观察法的光通信接收端优化策略汽车实用技术(2022年5期)2022-04-02STM32和51单片机寄存器映射原理异同分析有色金属设计(2022年4期)2022-02-04顶管接收端脱壳及混凝土浇筑关键技术石家庄铁路职业技术学院学报(2021年1期)2021-06-09基于多接收线圈的无线电能传输系统优化研究科学技术创新(2021年7期)2021-03-23敷设某种吸声材料的声诱饵简化模型隔离度仿真计算声学技术(2020年4期)2020-09-15Lite寄存器模型的设计与实现计算机应用(2020年5期)2020-06-07数字电子时钟逻辑电路的教学设计与仿真电子制作(2019年20期)2019-12-04移位寄存器及算术运算应用电子技术与软件工程(2018年1期)2018-03-22基于软件技术的组合逻辑电路模型分析与实现研究中央民族大学学报(自然科学版)(2016年3期)2016-06-27短区间自动闭塞车站接近区段逻辑电路设计铁道通信信号(2016年2期)2016-06-01